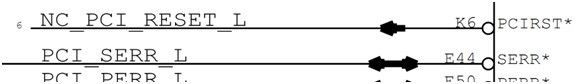

G3:查EC待机条件、RTC电路、公共点

S5:单桥待机条件

S3:包含内存供电等其他S3状态供电

S0:包含桥供电、总线供电、CPU供电以及其他S0状态的3.3v,5v等供电

PG、时钟、复位

G3:查EC待机条件、RTC电路、公共点

EC待机条件包括:待机供电、时钟、复位、程序

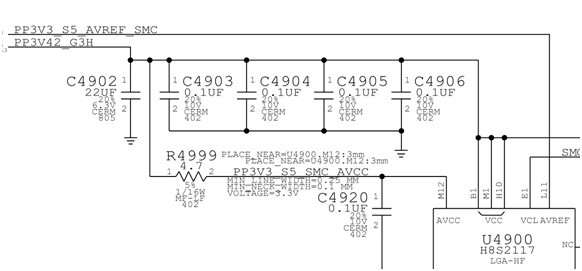

待机供电:主待机电压AVCC来自于PP3V42_G3H,同时给

VCC供电

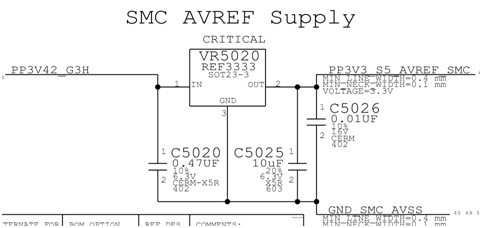

而AVREF来自于PP3V3_S5_AVREF_SMC,追查PP3V3_S5_AVREF_SMC来自于VR5020,工作原理是PP3V42_G3H给其供电,就可以输出PP3V3_S5_AVREF_SMC。所以说,PP3V3_S5_AVREF_SMC也是在待机时候就有!

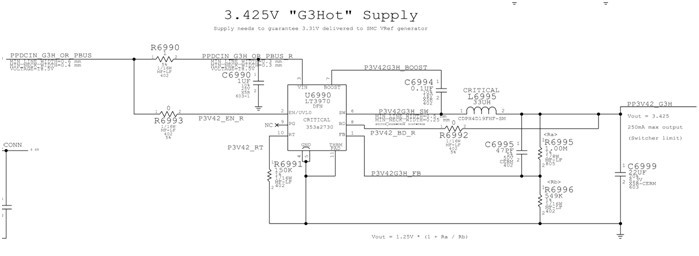

PP3V42_G3H由U6990,LT3970控制输出,这是一个微型PWM控制芯片,内部集成了上下管。引脚定义:VIN供电、EN开启、RT震荡设定、BOOST启动自举升压脚、SW相位/输出脚、FB反馈、BD连接内部升压二极管和稳压器

芯片的工作条件是VIN和EN,都来自于PPDCIN_G3H_OR_PBUS,追查PPDCIN_G3H_OR_PBUS来源:

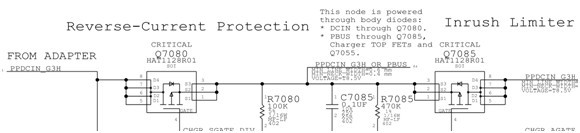

PPDCIN_G3H_OR_PBUS由Q7080或Q7085提供,具体:插入适配器产生PPDCIN_G3H,经过Q7080的体二极管产生PPDCIN_G3H_OR_PBUS,电池模式下,由电池经过Q7085的体二极管供电(备注:电池是先经过Q7055体二极管,再经过充电电路的上管Q7030的体二极管到达Q7085的5678脚)

EC待机供电流程小结:插入适配器或者电池经过各自场管的体二极管产生PPDCIN_G3H_OR_PBUS,供给U6990产生PP3V42_G3H给EC供电,并且经过VR5020产生PP3V3_S5_AVREF_SMC也给EC供电(基准电压)

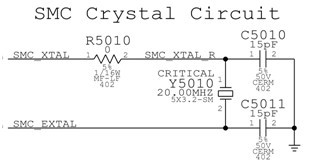

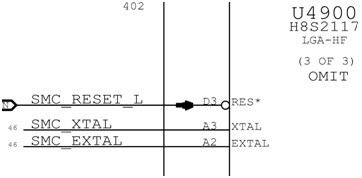

EC得到待机供电后,给Y5010供电,产生20M时钟给EC。

宋体;mso-fareast-theme-font: minor-fareast;mso-hansi-font-family:Calibri;mso-hansi-theme-font:minor-latin'>的体二极管到达Q7085的5678脚)

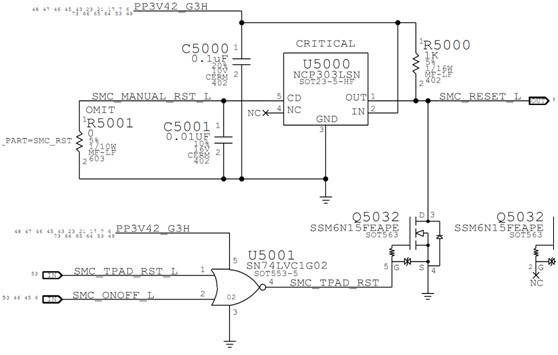

EC待机复位SMC_RESET_L来自于U5000,工作原理:2脚输入电压,给5脚C5001充电,当电压上升到超过阀值后,OUT脚开漏输出,由R5000上拉成3.42给EC复位。U5000是个电压检测/延时芯片。

t-family:Calibri;mso-ascii-theme-font:minor-latin; mso-fareast-font-family:宋体;mso-fareast-theme-font:minor-fareast;mso-hansi-font-family: Calibri;mso-hansi-theme-font:minor-latin'>时钟给EC。宋体;mso-fareast-theme-font: minor-fareast;mso-hansi-font-family:Calibri;mso-hansi-theme-font:minor-latin'>的体二极管到达Q7085的5678脚)

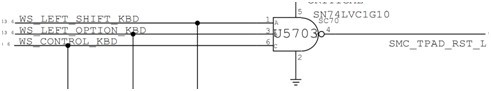

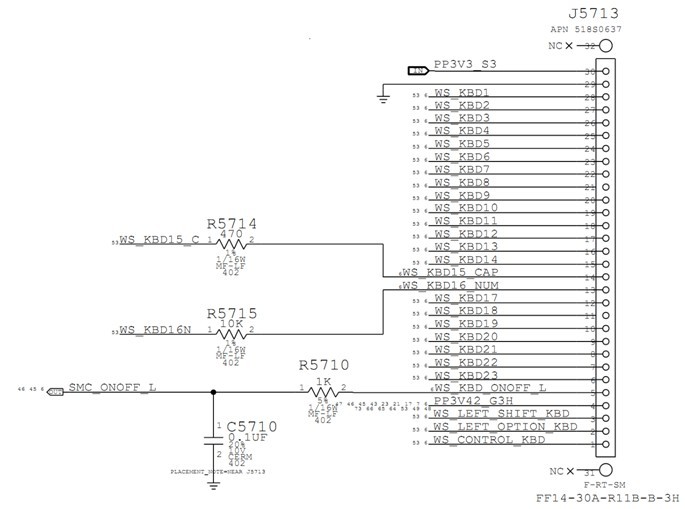

可以通过U5001和Q5032的电路实现强制复位EC:同时按下左边的SHIFT+左边的OPTION+CONTROL+开机键

EC自带程序。不需要读取BIOS

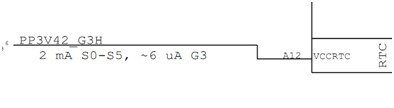

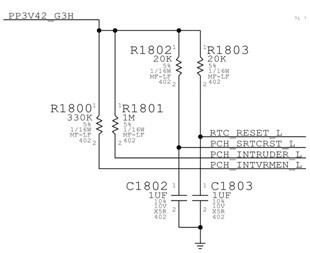

RTC电路主要条件:VCCRTC、RTCRST#、SRTCRST#、32.768KHz

VCCRTC来源由PP3V42_G3H直接供电,此机没有CMOS电池!

RTCRST#、SRTCRST#都由下面电路延时而来,RTC电路另外2个信号是INTRUDER#和INTVRMEN则由3.42V上拉

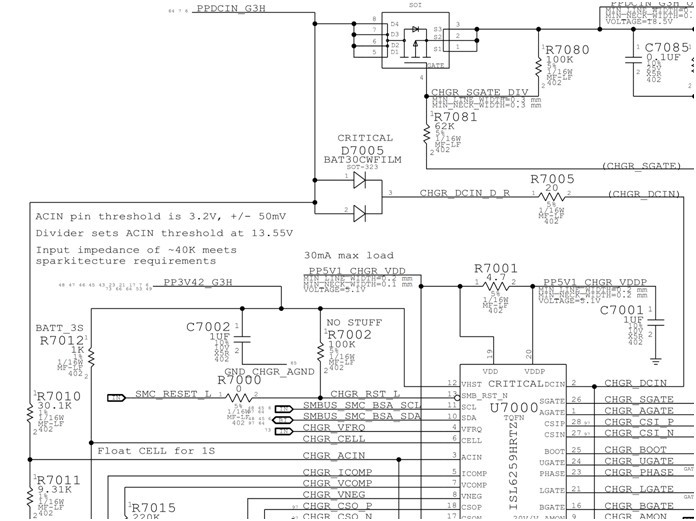

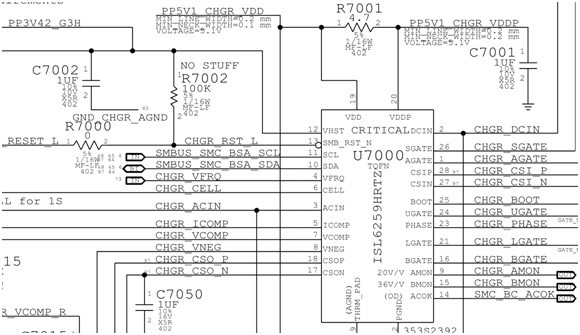

适配器检测具体流程:DCIN供电à输出VDD线性电压5.1và返回给VDDP供电àACIN电压若超过3.2vàACOK开漏输出à由PP3V42_G3H经过R5087上拉为3.42v。

DCIN由PPDCIN_G3H经过D7005、R7005供电,ACIN由PPDCIN_G3H经过R7010和R7011分压与内部3.2V比较

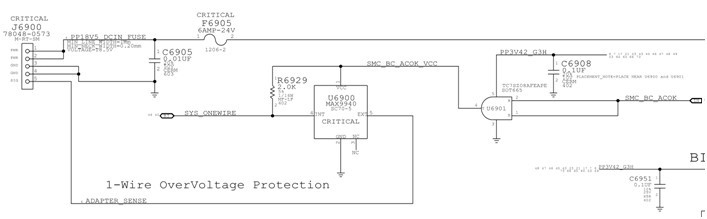

SMC_BC_ACOK一路送给EC表示适配器插入另一路送给与门U6901产生SMC_BC_ACOK_VCC给U6900供电。

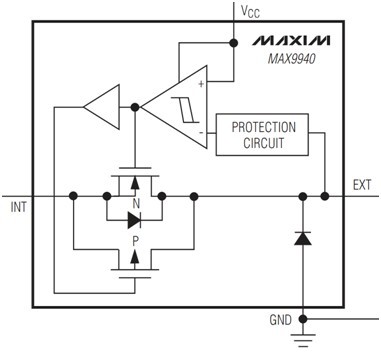

U6900是一个信号线过压保护器,可用于防静电,简单原理:当EXT电压不低于-0.7v不超过28V时,芯片把4脚和5脚连通,也就是把适配器接口J6900的5脚连通到SYS_ONEWIRE,这是一条单线串行总线,叫ONE-WIRE。用于传输适配器信息,DELL也用的这种方式。当EC通过ONE-WIRE总线读取到适配器参数后,适配器头上的绿灯就亮了。。。

U6900内部结构:

小知识:关于ONE-WIRE---美国的达拉斯半导体公司(DALLASSEMICONDUCTOR)推出的一项特有的单总线(1-Wire Bus)技术。该技术与SPI、I2C、SCI总线不同,它采用单根信号线,既可传输时钟,又能传输数据,而且数据传输是双向的,因而这种单总线技术具有线路简单,硬件开销少,成本低廉,便于总线扩展和维护等优点。

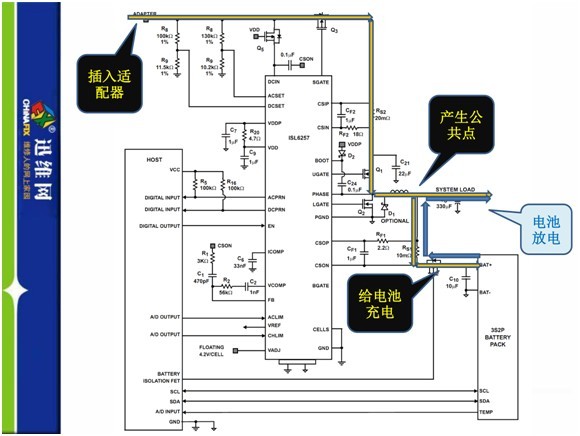

公共点:

苹果的公共点产生方式与其他不同。它采取的是这种混合供电方案:由适配器经过充电芯片的调节产生公共点,若有需要再给电池充电

公共点由充电芯片ISL6259控制输出,主要工作条件:DCIN、ACIN、SCL/SDA、CELL、VHST、SMB_RST_N

S5:单桥待机条件

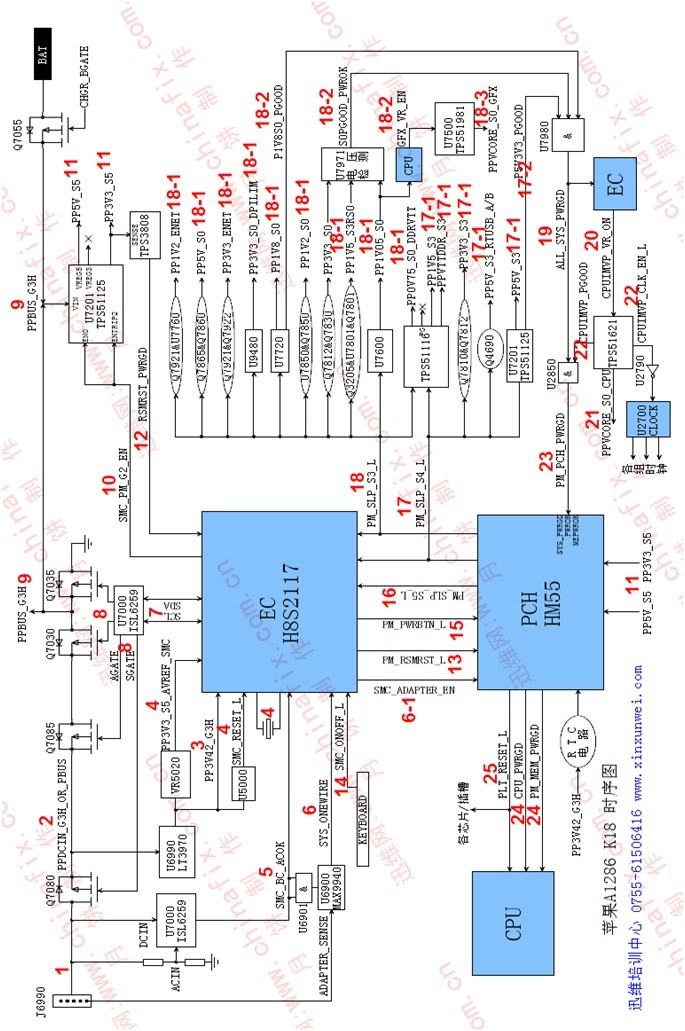

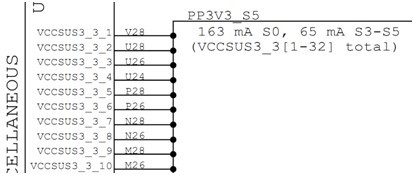

单桥待机条件包含:VCCSUS3_3、V5REF_SUS、RSMRST#、PWRBTN#

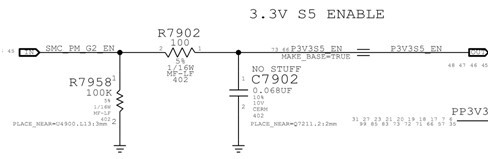

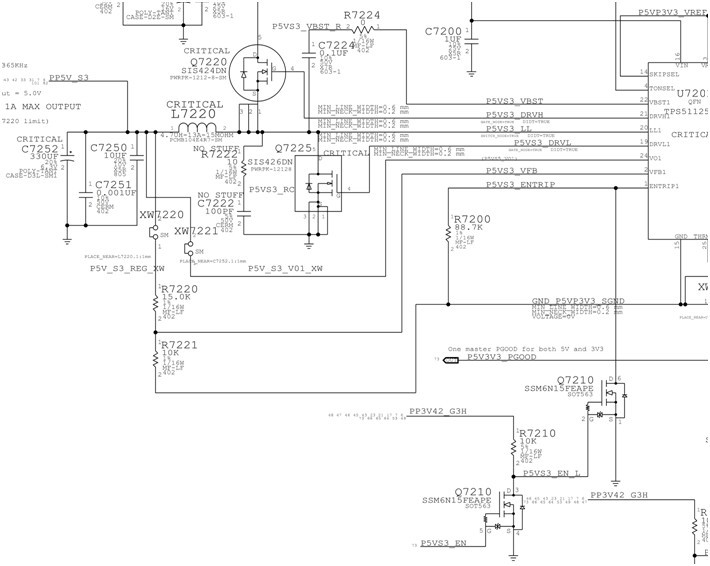

单桥的3.3v待机电压VCCSUS3_3在苹果中的名字是PP3V3_S5

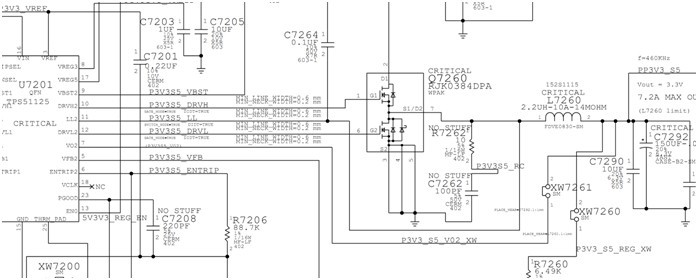

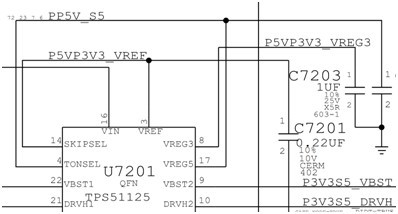

来源于TPS51125控制,开启脚是ENTRIP2,对应名字是P3V3S5_ENTRIP。(待机时只有一个3.3v电感有电,5v没有)

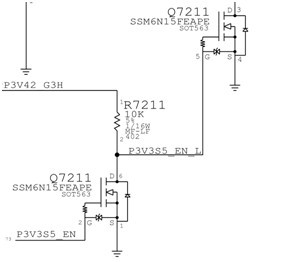

6脚ENTRIP2受控于Q7211,最终受控于P3V3S5_EN。(TPS51125的6脚定义是直接接地关闭输出,通过电阻接地作为过流限制设定脚,如果P3V3S5_EN为低电平,Q7211的6-1脚截止,3-4就会导通,拉低ENTRIP2,关闭输出;如果P3V3S5_EN为高电平,Q7211的6-1脚导通,3-4脚截止,TPS51125内部给ENTRIP2提供上拉,与R7206分压成高电平开启芯片,并设定过流限值。)

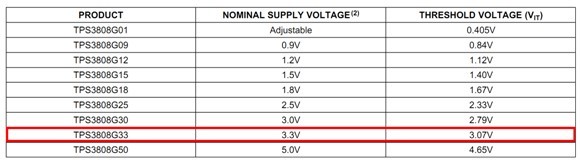

TPS51125的ENTRIP2的门槛值:

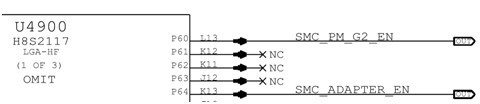

P3V3S5_EN由SMC_PM_G2_EN转换而来

SMC_PM_G2_EN由EC发出(EC检测到适配器存在,跟适配器正常通信后,发出的;EC检测到适配器后还会发出SMC_ADAPTER_EN给PCH,告诉PCH适配器已经插入)

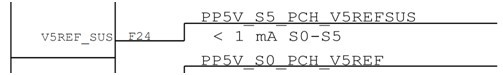

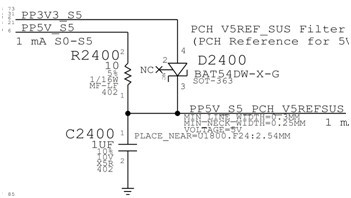

单桥的5v待机电压V5REF_SUS在苹果中的名字是PP5V_S5_PCH_V5REFSUS

TPS51125输出线性电压的条件是主供电VIN来自于公共点、EN0由SMC_PM_G2_EN供给。

S5状态供电的小结:公共点给TPS51125供电,EC发出SMC_PM_G2_EN开启线性5v和3.3v,线性5v作为单桥的5V待机电压,线性3.3v不用。同时SMC_PM_G2_EN还通过转换控制3.3V的PWM供电作为单桥的3.3V待机电压。

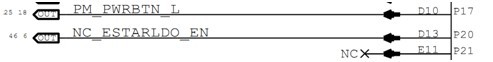

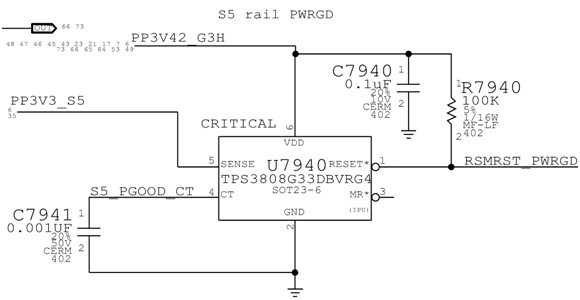

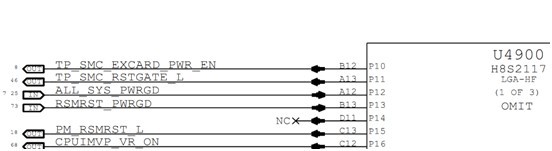

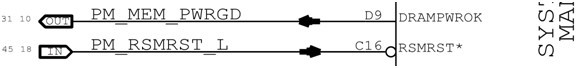

单桥RSMRST#对应名称PM_RSMRST_L,来源于EC,EC是需要收到RSMRST_PWRGD才发出给单桥的。

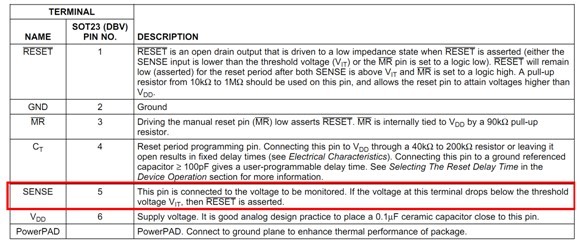

根据其引脚定义知道检测5脚电压,当此脚低于阀值VIT,RESET#有效!

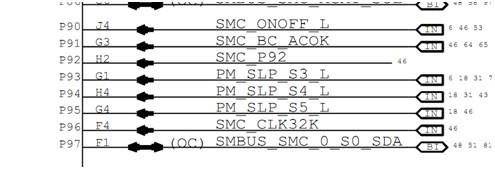

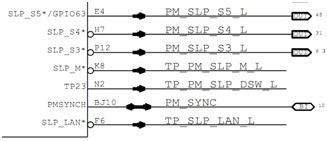

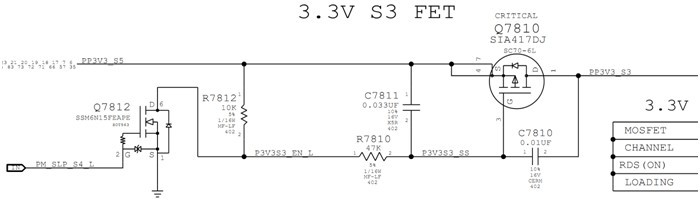

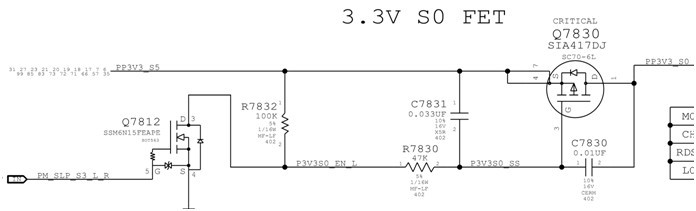

PM_SLP_S5_L送给EC;PM_SLP_S4_L也给EC,同时还给Q7812经过转换控制产生PP3V3_S3电压

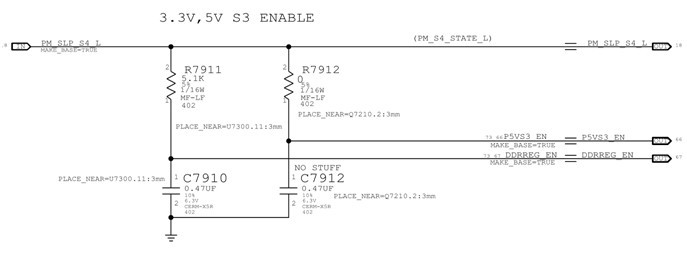

PM_SLP_S4_L还转换成P5VS3_EN和DDRREG_EN

i

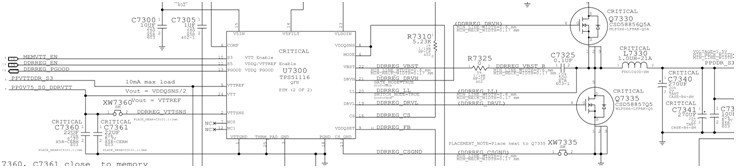

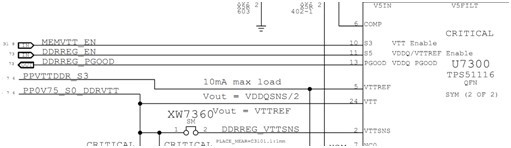

DDRREG_EN送给TPS51116的S5脚,这是一个典型的内存供电芯片,它会输出PWM供电PP1V5_S3和PPVTTDDR_S3

内存主供电和基准电压正常后,TPS51116会输出DDRREG_PGOOD送给73页的检测电路,我叫它“大与门”

P5VS3_EN经过转换控制TPS51125的1脚,用于控制产生PP5V_S3

PP5V_S3正常后,TPS51125才会发出P5V3V3_PGOOD,也是送给73页的检测电路。(前面所说的3.3V出来后,TPS51125的PG并不会输出,只有当5V也正常后,它会开漏输出PGOOD!)

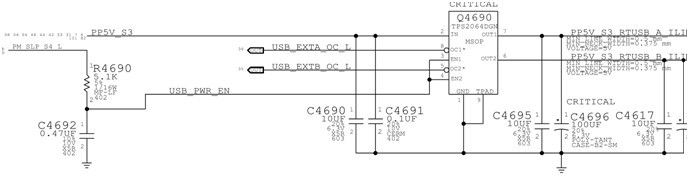

PM_SLP_S4_L还用于控制USB供电

S0:包含桥供电、总线供电、CPU供电以及其他S0状态的3.3v,5v等供电

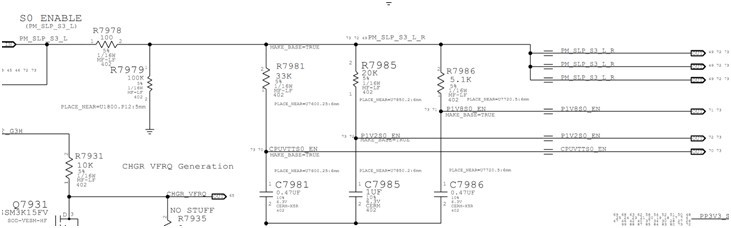

单桥发出的SLP_S3#,更名为PM_SLP_S3_L,除了送给EC外,还送给下面这些地方:

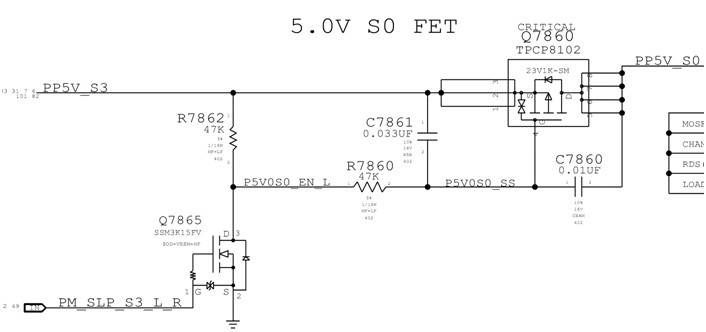

控制产生PP5V_S0

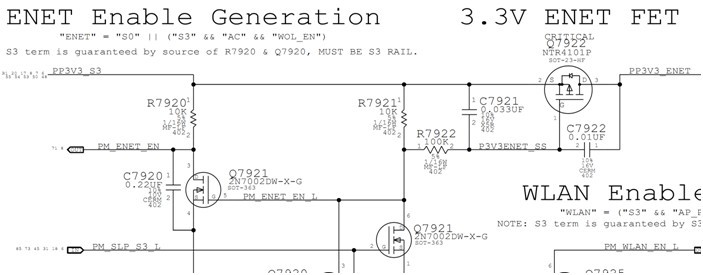

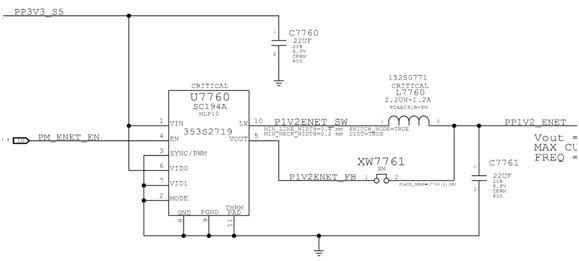

控制开启3.3v的网卡供电PP3V3_ENET,并产生PM_ENET_EN

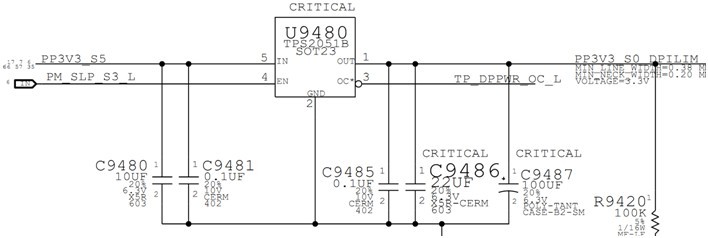

控制开启U9480产生PP3V3_S0_DPILIM给J9400供电

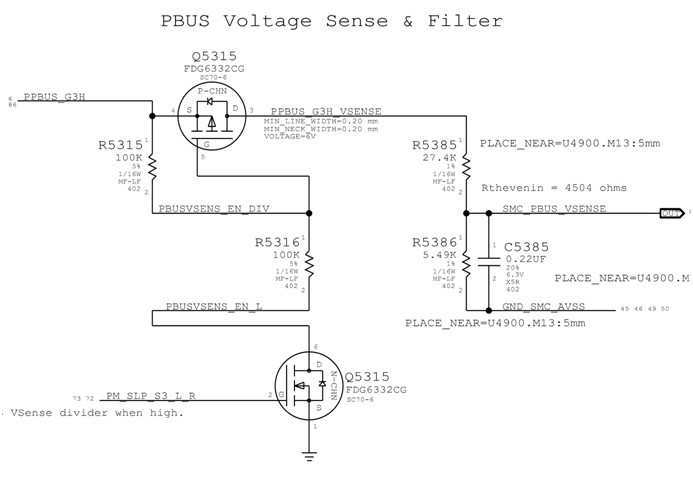

控制开启公共点电压检测电路

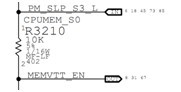

通过电阻R3210转换为MEMVTT_EN,去开启内存的PP0V75_S0_DDRVTT

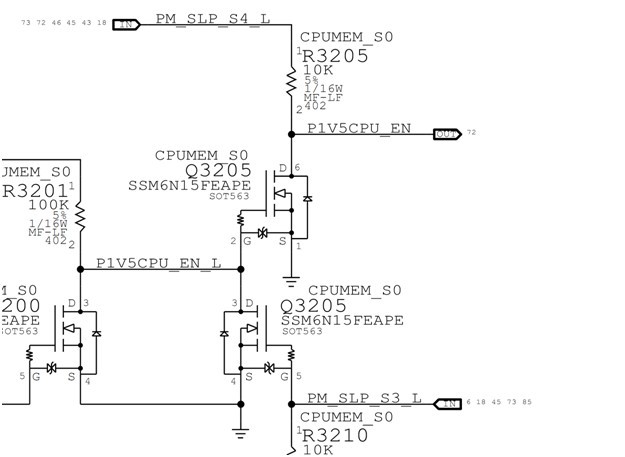

还会通过下面这个电路转换出P1V8S0_EN、P1V2S0_EN、CPUVTTS0_EN、以及P1V5CPU_EN

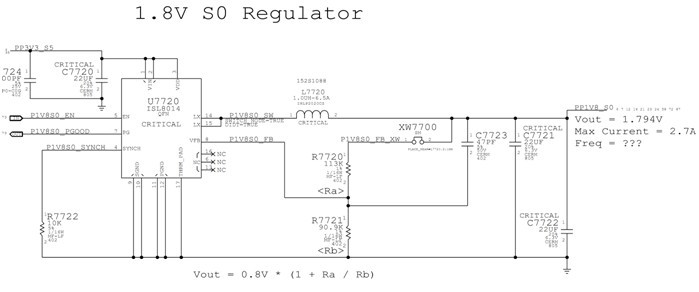

其中P1V8S0_EN送给U7720开启PP1V8_S0

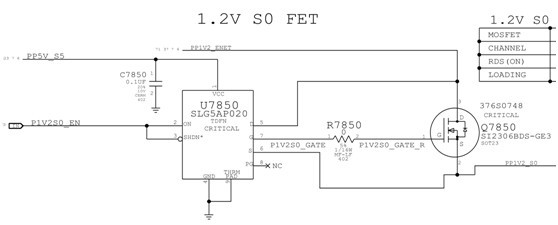

P1V2S0_EN送给U7850,使之发出7脚的控制信号驱动Q7850产生PP1V2_S0

Q7850的输入电压1V2_ENET是由PM_ENET_EN控制U7760输出的

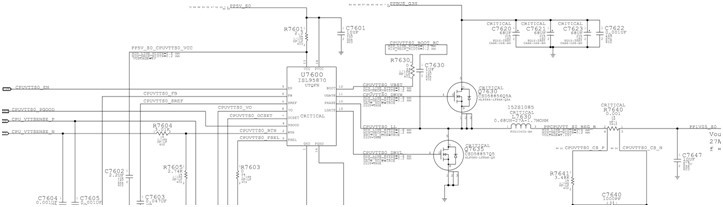

CPUVTTS0_EN送给U7600控制输出PP1V05_S0

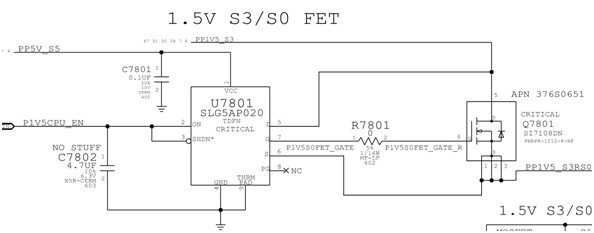

P1V5CPU_EN送给U7801,控制Q7801把内存的PP1V5_S3供电转换为PP1V5_S3_RS0给CPU供电

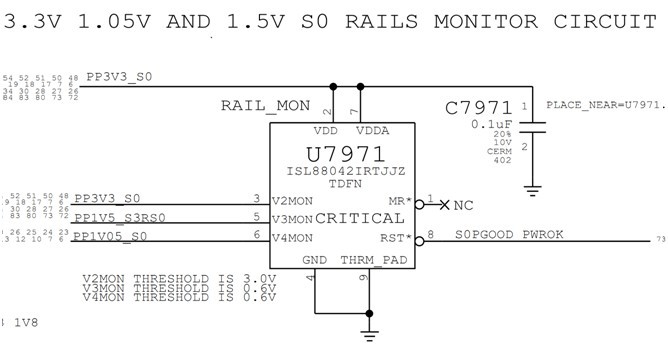

先由U7971检测PP3V3_S0、PP1V5_S3RS0、PP1V05_S0,超过各自的阀值后,RST#开漏输出S0PGOOD_PWROK

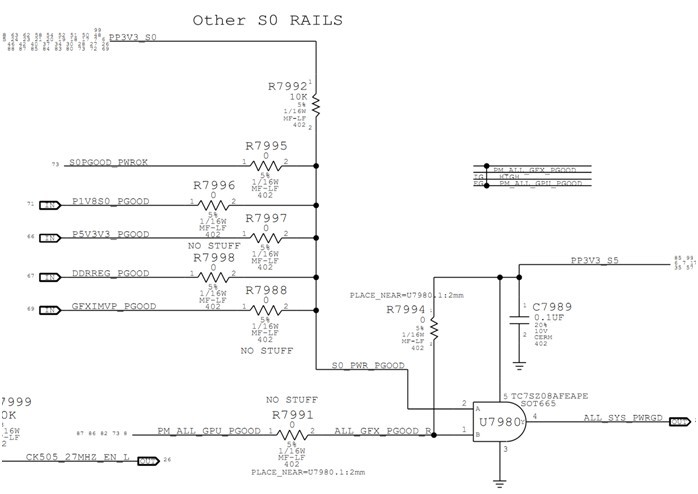

S0PGOOD_PWRO再与其它供电芯片开漏输出的PG相与“大与门”,由PP3V3_S0上拉生成S0_PWR_PGOOD

再由S0_PWR_GOOD送给U7980,和PP3V3_S5上拉的ALL_GFX_PGOOD相与,共同产生ALL_SYS_PWRGD

(R7991没有安装零件)

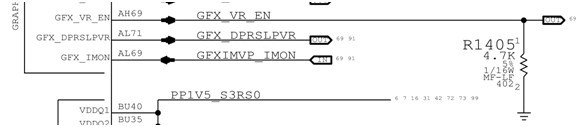

其中总线供电产生后,给CPU供电,CPU会发出GFX_VR_EN开启CPU内集成显卡供电

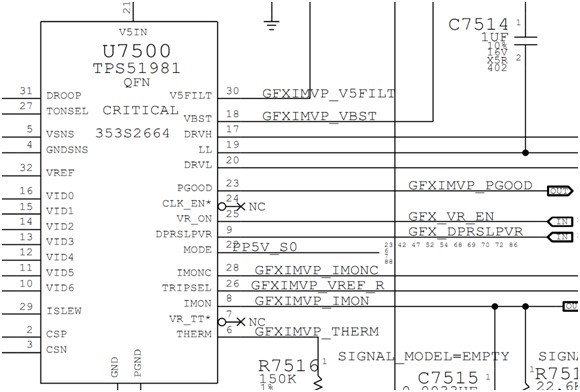

GFX_VR_EN是送给U7500 TPS51981的25脚,集显供电正常后的PG输出后连接的电阻没有安装,不采用此路PG。

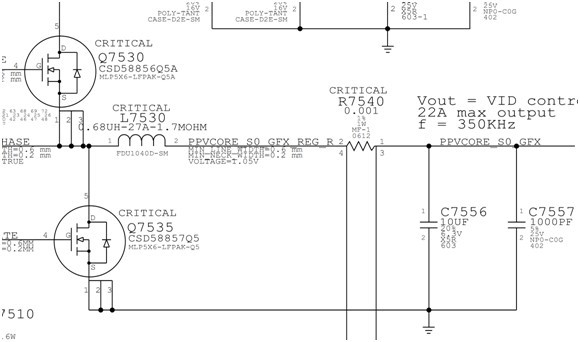

输出的集显供电名字是:PPVCORE_S0_GFX

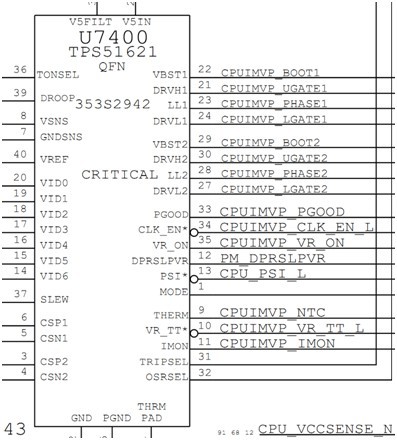

CPUIMVP_VR_ON送给U7400 TPS51621的35脚,开启CPU供电n>16脚,暂时还未开启。)

PG、时钟、复位

CPU供电正常后,发出CPUIMVP_PGOOD和CPUIMVP_CLK_EN_L

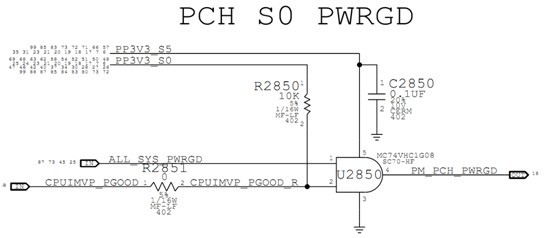

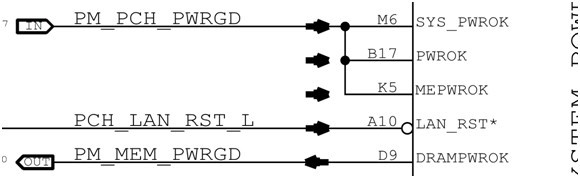

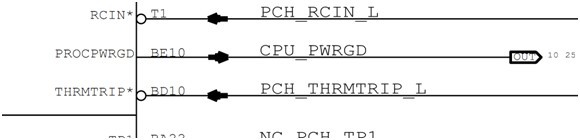

CPUIMVP_PGOOD送给U2850与ALL_SYS_PWRGD相与,形成PM_PCH_PWRGD送给桥

ma'>电压的PG连接!)

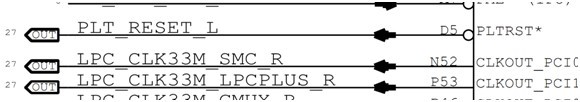

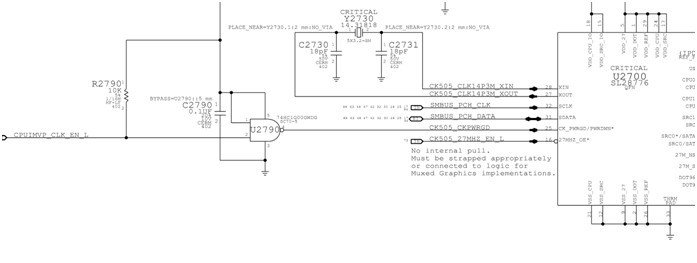

CPUIMVP_CLK_EN_L经过U2790这个与非门反相后,送给U2700时钟芯片开启各路时钟(27M受控于16脚,暂时还未开启。)

最后,PCH满足了供电、时钟、PG后,发出DRAMPWROK、PROCPWRGD给CPU,

发出PLTRST#给各板载芯片和插槽,PCIRST#空置。